в пакете заранее не опре-

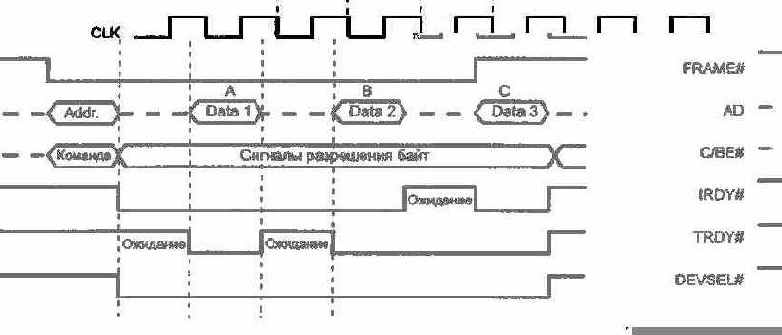

Рисунок 4.9. Цикл обмена на шине РС1

Количество фаз (циклов) данных в пакете заранее не опре- делено, но перед последним циклом ИУ при введенном сиг- нале IRDY# снимает сигнал FRAMED. После последней фазы данных ИУ снимает сигнал IRDY#, и шина переходит в со- стояние покоя (PCI Idle) - оба. сигнала FRAME# и IRDY# на- ходятся в пассивном состоянии. Максимальное количество

циклов данных в пакете может быть неявно ограничено тай- мером, определяющим максимальное время, в течение кото- рого И У может пользоваться шиной. И У завершает тран- закцию одним из следующих способов:

Нормальное завершение выполняется по окончании об- мена данными.

Завершение по тайм-ауту (Time-out) происходит, когда во время транзакции у ИУотбирают право на управле- ние шиной (снятием сигнала GNT#) или когда истекает время, указанное в его таймере MLT (медленное ЦУ или слишком длинная транзакция).

Транзакция отвергается (Abort), когда в течение заданно- го времени ИУ не получает ответа ЦУ (DEVSEL#).

Транзакция может быть прекращена и по инициативе ЦУ, для этого оно может ввести сигнал STOP#. Возможны три типа прекращения:

Отключение (Disconnect) - сигнал STOP# вводится во время активности TRDY#. В этом случае транзакция за- вершается после фазы данных.

Отключение с повтором (Disconnect/Retry) - сигнал STOP# вводится при пассивном состоянии TRDY#, и по- следняя фаза данных отсутствует. Является указанием ИУ на необходимость повтора транзакции.

Отказ (Abort) - сигнал STOP# вводится одновременно со снятием DEVSEL# (в предыдущих случаях во время по- явления сигнала STOP# сигнал DEVSEL был активен). В этом случае последняя фаза данных тоже отсутствует, но повтор не запрашивается.

Протокол квитирования обеспечивает надежность обмена - ИУ всегда получает информацию об отработке транзакции ЦУ. Средством повышения надежности (достоверности) яв- ляется применение контроля паритета: линии AD[31:0] и С/ВЕ#[3:0] и в фазе адреса, и в фазе данных защищены битом паритета PAR (количество единичных бит этих линий, вклю- чая PAR, должно быть четным).

Действительное значение PAR появляется на шине с задержкой в один такт относительно линий AD и С/ВЕ#. При обнаружении ошибки ЦУ со сдви-

том на такт вырабатывается сигнал PERFW. В подсчете пари- тета при передаче данных учитываются все байты, включая и недействительные (отмеченные высоким уровнем сигнала C/BE#i). Состояние бит и недействительных байт данных во время фазы данных должно оставаться стабильным.

Арбитражем запросов на использование шины занимается специальный узел, входящий в чипсет системной платы. Каж- дое ИУ имеет пару сигналов - REQft для запроса на управ- ление шиной и GNT# для подтверждения предоставления управления шиной. Схема приоритетов (фиксированный, циклический, комбинированный) определяется программи- рованием арбитра.

Каждое устройство - потенциальное ИУ (PCIMaster) - име- ет собственный программируемый таймер MLT (Master Latency Timer), определяющий максимальное количество так- тов шины, допустимое для одной транзакции. Его конфигу- рированием осуществляется распределение полосы пропус- кания шины между устройствами.

Каждое ЦУ имеет инкрементный механизм слежения за дли- тельностью циклов (Incremental Latency Mechanism), который не позволяет интервалу между соседними фазами данных в пакете превышать 8 тактов шины. Если ЦУ не успевает ра- ботать в таком темпе, оно обязано остановить транзакцию.

Адресация памяти, портов и конфигурационных регистров различна. Байты шины AD, несущие действительную инфор- мацию, выбираются сигналами С/ВЕ[3:0] в фазах данных (внутри пакета эти сигналы могут менять состояние). В цик- лах обращения к памяти адрес, выровненный по границе двойного слова, передается по линиям AD[31:2], линии AD[1:0] задают порядок чередования адресов в пакете:

00 - линейное инкрементирование;

01 - чередование адресов с учетом длины строки кэш- памяти;

1х -зарезервировано.

В циклах обращения к портам ввода/вывода для адресации любого байта используются все линии AD[31:0]. В циклах конфигурационной записи/считывания устройство выбира-

ется индивидуальным сигналом IDSEL#, конфигурационные регистры выбираются двойными словами по линиям AD[7:2], при этом AD[1:0]=00. Сигнал выборки IDSEL# воспринима- ется устройством только в фазе адреса, поэтому обычно в качестве него используют старшие биты адреса с позицион- ным кодированием адреса устройства.

Команды шины PCI определяются значениями бит С/ВЕ# в фазе адреса в соответствии с табл. 4.5.

|

С/ВЕ[3:0] |

Тип команды |

|

0000 |

Interrupt Acknowledge - подтверждение прерывания |

|

0001 |

Special Cycle - специальный цикл |

|

0010 |

I/O Read - чтение порта ввода/вывода |

|

0011 |

I/O Write - запись в порт ввода/вывода |

|

0100 |

Зарезервировано |

|

0101 |

Зарезервировано |

|

0110 |

Memory Read - чтение памяти |

|

0111 |

Memory Write - запись в память |

|

1000 |

Зарезервировано |

|

1001 |

Зарезервировано |

|

1010 |

Configuration Read - конфигурационное считывание |

|

1011 |

Configuration Write - конфигурационная запись |

|

1100 |

Multiple Memory Read - множественное чтение памяти |

|

1101 |

Dual Address Cycle - двухадресный цикл |

|

1110 |

Memory Read Line - чтение строк памяти |

|

1111 |

Memory Write and Invalidate - запись с инвалидацией |

Специальный цикл декодируется содержимым линий AD[15:0] и используется для указания на отключение (Shutdown), ос- танов (Halt) процессора или специфические функции процес- сора, связанные с кэшем и трассировкой. Этим состояниям соответствуют коды 0000, 0001 и 0002; коды 0003-FFFFh за- резервированы.

В командах чтения и записи ввода/вывода линии AD содер- жат адрес байта, причем декодированию подлежат и биты ADO и AD1 (несмотря на то, что имеются сигналы ВЕх#). Порты PCI могут быть 8-, 16- или 32-битными. Для адреса- ции портов на шине PCI доступны все 32 бита адреса, но процессоры х86 могут использовать только младшие 16 бит. Порты с адресами OCF8 и OCFC зарезервированы под реги- стры адреса и данных для доступа к конфигурационному пространству.

Обращение к порту данных приведет к гене- рации шинного цикла конфигурационного чтения или за- писи по предварительно записанному адресу.

В командах чтения и записи памяти шина AD содержит ад- реса двойных слов, и линии ADO, AD1 не должны декодиро- ваться - на конкретные байты указывают сигналы С/ ВЕ[3:0]#.

Команды конфигурационного чтения и записи адресуются к конфигурационному пространству и обеспечивают доступ к 256-байтным структурам. Обращение производится двой- ными словами. Структура содержит идентификатор устрой- ства и производителя, состояние и команду, информацию об используемых ресурсах и ограничения на использование шины.

Множественное чтение памяти используется для транзак- ций, пересекающих границы строк кэш-памяти.

Двухадресный цикл применяется, когда физическая шина имеет 32 бита адреса, а требуется передача с 64-битной ад- ресацией. В этом случае младшие 32 бита адреса передают- ся в цикле данного типа, а за ним следует обычный цикл, определяющий тип обмена и несущий старшие 32 бита ад- реса. Шина PCI допускает 64-битную адресацию даже для портов ввода/вывода (для х86 это бесполезно, но PCI суще- ствует и на других платформах).

Чтение строк памяти применяется, когда в транзакции пла- нируется более двух 32-битных передач (обычно это чтение до конца строки кэша).

Запись с инвалидацией применяется к целым строкам кэша и позволяет оптимизировать циклы обратной записи "гряз- ных" строк кэша.

Выделение специальных циклов множественного чтения, чтения строк и записи с инвалидацией позволяет контрол- леру памяти предпринять определенные меры для оптими- зации данных передач.

Слоты PCI с шагом 0,05 дюйма расположены несколько даль- ше от задней панели, чем ISA/EISA или МСА. Компоненты карт PCI расположены на левой поверхности плат. По этой причине крайний PCI-слот обычно разделяет использование посадочного места адаптера с соседним ISA-слотом (Shared slot). Шина имеет версии с питанием 5 В, 33 В и универ- сальную (с переключением линий +V I/O с 5 В на 3,3 В).Клю- чами являются пропущенные ряды контактов 12, 13 и 50, 51. Для слота на 5 В ключ расположен на месте контактов 50, 51;

для 3 В - 12, 13; для универсального - два ключа: 12, 13 и 50, 51. Ключи не позволяют установить карту в слот с не- подходящим напряжением питания, 32-битный слот закан- чивается контактами А62/В62, 64-битный - А94/В94. На Рисунок 4.10 изображена 32-битная плата максимального размера (Long Card), длина короткой платы (Short Card) - 6,875". Плата может иметь обрамление (скобки), стандартное для конструктива ISA или МСА. Назначение выводов универ- сального разъема приведено в табл. 4.6, назначение сигна- лов - в табл. 4.7.