Карта расширения для шины PCI

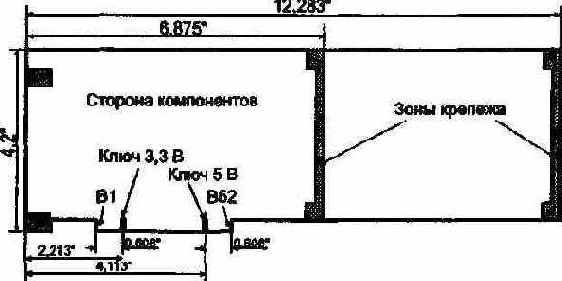

Рисунок 4.10. Карта расширения для шины PCI

На одной шине PCI может быть не более четырех устройств (следовательно, и слотов). Для подключения к другим ши- нам применяются специальные аппаратные средства - мос-

ты PCI (PCI Bridge). Главный мост (Host Bridge) использу- ется для подключения PCI к системной шине. Одноранго- вый мост (Peer-to-Peer Bridge) используется для соединения двух шин PCI. Несколько шин PCI применяются в серве- рах - это позволяет увеличить число подключаемых уст- ройств. Для подключения шин ISA/EISA используются спе- циальные мосты, входящие в чипсеты системных плат. Каждый мост программируется - ему указываются диапа- зоны адресов пространств памяти и ввода/вывода, отведен- ные устройствам его шин. Если адрес ЦУ текущей транзак- ции на одной шине (стороне) моста относится к шине противоположной стороны, мост перенаправляет транзакцию на соответствующую шину и выполняет действия по согла- сованию протоколов шин. Таким образом, совокупность мо- стов PCI выполняет маршрутизацию (routing) обращений по связанным шинам. Считается, что устройство с конкретным адресом может присутствовать только на одной из шин, а на какой именно, "знают" запрограммированные мосты. Ре- шать задачу маршрутизации призван также сигнал DEVSEL#. Обращения, не востребованные абонентами PCI, обычно пе- ренаправляются на шину ISA/EISA.

| Ряд В | Nft | РЯДА | Ряд В | N# | РЯДА | ||||||

| -12 В | 1 | TRST# | PRSNT2# | 11 | Reserved | ||||||

| тек | 2 | +12 В | GND/Ключ 3,3В | 12 | GND/Ключ 3,3В | ||||||

| GND | 3 | TMS | GND/Ключ 3,3В | 13 | GND/Ключ 3,3В | ||||||

| TDO | 4 | TDI | Reserved | 14 | Reserved | ||||||

| +5 В | 5 | +5 В | GND | 15 | RST# | ||||||

| +5 В | 6 | INTRA# | Clock | 16 | +VI/0 | ||||||

| INTRB# | 7 | INTRC# | GND | 17 | GNT# | ||||||

| INTRD# | 8 | +5 В | REQ# | 18 | GND | ||||||

| PRSNT1# | 9 | Reserved | +VI/0 | 19 | Reserved | ||||||

| Reserved | 10 | +VI/0 | AD 31 | 20 | AD 30 |

| Ряд В | N# | РЯДА | Ряд В | N# | РЯДА |

| AD 29 | 21 | +3,3 В | GND/Ключ 5В | 50 | GND/Ключ 5В |

| GND | 22 | AD 28 | GND/Ключ 5В | 51 | GND/Ключ 5В |

| AD 27 | 23 | AD 26 | AD8 | 52 | С/ВЕО# |

| AD 25 | 24 | GND | AD7 | 53 | +3,3 В |

| +3,3 В | 25 | AD 24 | +3,3 В | 54 | AD 6 |

| С/ВЕЗ# | 26 | IDSELff | AD5 | 55 | AD 4 |

| AD 23 | 27 | +3,3 В | AD3 | 56 | GND |

| GND | 28 | AD 22 | GND | 57 | AD 2 |

| AD 21 | 29 | AD 20 | AD 1 | 58 | ADO |

| AD 19 | 30 | GND | +VI/0 | 59 | +VI/0 |

| +3.3 В | 31 | AD 18 | АСК64# | 60 | REQ64# |

| AD 17 | 32 | AD 16 | +5 В | 61 | +5 В |

| С/ВЕ2# | 33 | +3,3 В | +5 В | 62 | +5 В |

| GND | 34 | FRAMED | Конец 32-битного разъема | ||

| IRDY# | 35 | GND | Reserved | 63 | GND |

| +3,3 В | 36 | TRDY# | GND | 64 | C/BE7# |

| DEVSEL# | 37 | GND | С/ВЕ6# | 65 | С/ВЕ5# |

| GND | 38 | STOP* | С/ВЕ4# | 66 | +VI/0 |

| LOCK* | 39 | +3,3 В | GND | 67 | PAR64 |

| PERR# | 40 | SDONE# | AD63 | 68 | AD 62 |

| +3,3 В | 41 | SDOFF | AD61 | 69 | GND |

| SERR# | 42 | GND | +VI/0 | 70 | AD 60 |

| +3,3 В | 43 | PAR | AD59 | 71 | AD 58 |

| С/ВЕ1# | 44 | AD 15 | AD57 | 72 | GND |

| AD 14 | 45 | +3,3 В | GND | 73 | AD 56 |

| GND | 46 | AD 13 | AD55 | 74 | AD 54 |

| AD 12 | 47 | AD 11 | AD53 | 75 | +VI/0 |

| AD 10 | 48 | GND | GND | 76 | AD 52 |

| GND/M66EN1 | 49 | AD 9 | AD51 | 77 | AD 50 |

| Ряд В | N" | РЯДА | Ряд В | Ntf | РЯДА |

| AD 49 | 78 | GND | AD 37 | 87 | GND |

| +VI/0 | 79 | AD 48 | +VI/0 | 88 | AD 36 |

| AD 47 | 80 | AD 46 | AD 35 | 89 | AD 34 |

| AD 45 | 81 | GND | AD 33 | 90 | GND |

| GND | 82 | AD 44 | GND | 91 | AD 32 |

| AD 43 | 83 | AD 42 | Reserved | 92 | Reserved |

| AD 41 | 84 | +VI/0 | Reserved | 93 | GND |

| GND | 85 | AD 40 | GND | 94 | Reserved |

| AD 39 | 86 | AD 38 | Конец 64-битного разъема |

' Сигнал M66EN определен в PCI 2.1.

|

Сигнал |

Назначение |

|

AD[31:0] |

Address/Data - мультиплексированная шина адре- са/данных. В начале транзакции передается адрес, в последующих тактах - данные |

|

C/BE[3:0]# |

Command/Byte Enable - команда/разрешение обра- щения к байтам. Команда, определяющая тип оче- редного цикла шины, задается четырехбитным кодом в фазе адреса |

|

FRAME* |

Кадр. Введением сигнала отмечается начало тран- закции (фаза адреса), снятие сигнала указывает на то, что последующий цикл передачи данных является последним в транзакции |

|

DEVSEL# |

Device Select - устройство выбрано (ответ ЦУ на адресованную ему транзакцию) |

|

IRDY# |

Initiator Ready - готовность И У к обмену данными |

|

TRDY# |

Target Ready - готовность ЦУ к обмену данными |

|

STOP# |

Запрос ЦУ к ИУ на останов текущей транзакции |

|

LOCK# |

Используется для установки, обслуживания и освобождения захвата ресурса PCI |

|

REQ# |

Request - запрос от PCI-мастера на захват шины |

|

GNT# |

Grant - предоставление мастеру управления шиной |

|

PAR |

Parity - общий бит паритета для линий AD[31:0] и С/ВЕ[3:0] |

|

Сигнал |

Назначение |

|

PERR# |

ParityError - сигнал об ошибке паритета (от устрой- ства, ее обнаружившего) |

|

PRSNT[1,2]# |

Present - индикаторы присутствия платы, коди- рующие запрос потребляемой мощности |

|

RSTft |

Reset - сброс всех регистров в начальное состояние |

|

IDSEL# |

Initialization Device Select - выбор устройства в циклах конфигурационного считывания и записи |

|

SERR |

System Error - системная ошибка. Активизируется любым устройством PCI и вызывает NMI |

|

REQ64# |

Request 64 bit - запрос на 64-битный обмен |

|

ACK64# |

Подтверждение 64-битного обмена |

|

INTRA# INTRB# INTRC# INTRD# |

Interrupt А, В, С, D - линии запросов прерывания. Циклически сдвигаются в слотах и направляются на доступные линии IRQ. Запрос по низкому уровню допускает разделяемое использование линий |

|

CLK |

Clock - тактовая частота шины. Должна быть в пределах 20-33 МГц, в PCI 2.1 - до 66 МГц |

|

M66EN |

66MHzEriable - разрешение частоты синхронизации до 66 МГц |

|

SDONE |

Snoop Done - сигнал завершенности цикла слежения для текущей транзакции. Низкий уровень указывает на незавершенность цикла слежения за когерент- ностью памяти и кэша. Необязательный сигнал, ис- пользуется только устройствами шины с кэшируемой памятью |

|

SBO# |

Snoop Backoff - попадание текущего обращения к памяти абонента шины в модифицированную строку кэша. Необязательный сигнал, используется только абонентами шины с кэшируемой памятью при алгоритме обратной записи |

|

TCK |

Test Clock - синхронизация тестового интерфейса JTAG |

|

TDI |

Test Data Input - входные данные тестового интерфейса JTAG |

|

TDO |

Test Data Output - выходные данные тестового интерфейса JTAG |

|

TMS |

Test Mode Select - выбор режима для тестового интерфейса JTAG |

|

TRST |

Test Logic Reset - сброс тестовой логики |

Одной из особенностей шины PCI является возможность обмена данными между процессором и памятью одновремен- но с обменом между другими устройствами PCI - Concurrent PCI Transferring. Эта возможность реализуется не всеми чип- сетами (в описаниях она всегда специально подчеркивает- ся), а обь1чными устройствами (видеокарты и контроллеры дисков) используется редко.

С мостами PCI/ISA связано понятие VGA Palette Snooping, которое обеспечивает исключение из правила однозначной маршрутизации обращений. Графическая карта в компью- тере с шиной PCI обычно устанавливается на шину PCI. На VGA-карте имеются регистры палитр (Palette Registers), при- писанные к пространству ввода/вывода. Если графическая система содержит еще и карту смешивания сигналов графи- ческого адаптера с сигналом "живого видео", перехватывая двоичную информацию о цвете текущего пиксела по шине VESA Feature Connector (снимаемую до регистра палитр), цветовая гамма будет определяться регистром палитр, раз- мещенным на этой дополнительной карте. Возникает ситуа- ция, когда операция записи в регистр палитр должна отра- батываться одновременно и в графическом адаптере (на шине PCI), и в карте видеорасширения, которая часто размещает- ся на шине ISA. В BIOS Setup может присутствовать опция PCI VGA Palette Snoop. При ее разрешении запись в порты ввода/вывода по адресу регистра палитр будет вызывать транзакцию как на шине PCI, так и на шине ISA, чтение же по этим адресам будет выполняться только PCI. Реализа- ция может возлагаться на графическую карту PCI. Для это- го она во время записи в регистр палитр фиксирует данные, но сигналы квитирования DEVSEL# и TRDY# не вырабаты- вает, в результате чего мост распространяет этот неопознан- ный запрос на шину ISA. В других реализациях мосту явно указывают на данное исключение, и он сам распространяет запись в регистры палитр на шину ISA.

Автоконфигурирование устройств (выбор адресов и преры- ваний) поддерживается средствами BIOS и ориентировано на технологию Plug and Play.

Стандарт PCI определяет для каждого слота конфигурационное пространство размером до 256 8-битных регистров, не приписанных ни к простран-

ству памяти, ни к пространству ввода/вывода. Доступ к ним осуществляется по специальным циклам шины Configuration Read и Configuration Write, вырабатываемым контроллером при обращении процессора к регистрам контроллера шины PCI, расположенным в его пространстве ввода/вывода. После аппаратного сброса (или по включении питания) устройства PCI не отвечают на обращения к пространству памяти и вво- да/вывода, они доступны только для операций конфигура- ционного считывания и записи. В этих операциях устрой- ства"'выбираются по индивидуальным сигналам IDSEL# и сообщают о потребностях в ресурсах и возможных диапазо- нах памяти. После распределения ресурсов, выполняемого программой конфигурирования (во время POST), в устрой- ства записываются параметры конфигурирования. Только после этого к устройствам становится возможным доступ по командам обращения к памяти и портам ввода/вывода.

Для ПЗУ расширения BIOS, установленных на картах PCI, принят стандарт, несколько отличающийся от традицион- ных дополнительных модулей ROM BIOS. Поскольку шина PCI используется не только в PC, в ПЗУ карты может хра- ниться несколько модулей. Тип платформы (процессора) указывается в заголовке модуля, и при инициализации BIOS активизируется нужный. Такой механизм позволяет, например, один и тот же графический адаптер устанавли- вать и в IBM PC, и в Power PC.

В состав шины PCI введены сигналы для тестирования адап- теров по интерфейсу JTAG. На системной плате эти сигналы задействованы не всегда, но они могут и организовывать ло- гическую цепочку тестируемых адаптеров.

Некоторые фирмы выпускают для PCI карты-прототипы, но доукомплектовать их адаптером собственной разработки сложнее, чем карту ISA. Здесь сказываются сложные прото- колы и высокие частоты.

Слот PCI достаточен для подключения адаптера (в отличие от VLB), на системной плате он может сосуществовать с любой из шин ввода/вывода и даже с VLB.

На некоторых системных платах позади одного из слотов PCI имеется разъем Media Bus, на который выводятся сигналы ISA. Он

используется для размещения на графическом адаптере PCI звукового чипсета, предназначенного для шины ISA.

Для устройств промышленного назначения в начале 1995 г. был принят стандарт Compact PCI. Шина Compact PCI (сРСГ) разрабатывалась на основе спецификации PCI 2.1. Эта шина отличается большим количеством поддерживаемых слотов:

8 против 4. Появились новые 4 пары сигналов запросов и предоставления управления шиной. Шина поддерживает 32-битный и 64-битный обмен (с индивидуальным разреше- нием байт). При частоте шины 33 МГц максимальная про- пускная способность составляет 133 Мбайт/с для 32 бит и 266 Мбайт/с для 64 бит (в середине пакетного цикла). Воз- можна работа на частоте 66 МГц. Шина поддерживает спе- цификацию РпР. Кроме того, в шине возможно применение географической адресации, при этом адрес модуля (на кото- рый он отзывается при программном обращении) определя- ется его положением в каркасе. Для этого на коннекторе J1 имеются контакты GAO...GA4, коммутацией которых на "зем- лю" для каждого слота задается его двоичный адрес. Геогра- фическая адресация позволяет переставлять однотипные мо- дули, не заботясь о конфигурировании их адресов (хорошая альтернатива системе РпР - модуль "встанет" всегда в одни и те же адреса, которые без физического вмешательства боль- ше не изменятся). Конструктивно платы Compact PCI пред- ставляют собой еврокарты высотой 3U (100х160 мм) с одним коннектором (J1) или 6U (233х160 мм) с двумя кон- некторами (J1 nJ2). Коннекторы - 7-рядные штырьковые разъемы с шагом 2 мм между контактами, на кросс-плате - вилка, на модулях - розетки. Контакты коннекторов имеют разную длину: более длинные контакты цепей питания при установке модуля соединяются раньше, а при вынимании разъединяются позже, чем сигнальные. Такое решение по- зволяет производить "горячую" замену модулей. Собствен- но шина использует только один коннектор (J1), причем в 32-битном варианте не полностью - часть контактов мо- жет задействовать пользователь, 64-битная шина использу- ет коннектор полностью.

Одно посадочное место на кросс- плате резервируется под контроллер шины, на который возлагаются функции арбитража и синхронизации. На его

коннекторе шиной используется большее число контактов, чем на остальных. У больших плат коннектор J2 предостав- ляется пользователю, а между коннекторами J 1 и J2 может устанавливаться 95-контактный коннектор J3. Конструкция коннекторов позволяет для J2 применять специфические мо- дификации (например, с разделяющим экраном и механи- ческими ключами). В шине предусматривается наличие не- зависимых источников питания +5 В, +3,3 В и ±12 В.

На базе шины Compact PCI фирмой National Instruments раз- работана спецификация PXI (PCI extensions for Instrumenta- tion - расширение PCI для инструментальных систем) в тех же конструктивах. В шине PXI часть контактов, определенных в Compact PCI как свободно используемые, предназначается для дополнительных шин. Шина Trigger Bus (8 линий) звез- дообразно соединяет слот своего контроллера (первый после системного контроллера PCI) с остальными слотами. Шина позволяет осуществлять синхронизацию разных модулей, что зачастую требуется в измерительных системах. Для прецизи- онной синхронизации имеется сигнал опорной частоты 10 МГц PXI_CLK, который звездообразно (с одинаковыми задержка- ми распространения сигнала) разводится по слотам. В PXI определены локальные шины, предназначенные для связи со- седних пар слотов. Каждая локальная шина имеет 13 линий, которые могут использоваться как для цифровых, так и для аналоговых (до 48 В) сигналов. Локальные шины объединя- ют смежные слоты попарно (исключая слот системного кон- троллера), образуя цепочку. Кроме механических и электри- ческих характеристик PXI определяет ПО модулей: основной ОС считается Windows NT/95, и модули должны поставляться с соответствующими драйверами. Это экономит время, необ- ходимое для системной интеграции. Модули PXI совмести- мы с шиной Compact PCI, и модули Compact PCI - с шиной PXI. Однако все преимущества спецификации реализуются только при установке модулей PXI в шину PXI.