Прием данных в байтном режиме

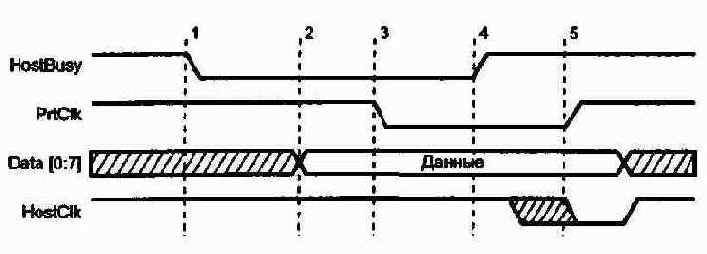

Рисунок 1.4. Прием данных в байтном режиме

Фазы приема байта данных:

1. Хост сигнализирует о готовности приема данных уста- новкой низкого уровня на линии HostBusy.

2. ПУ в ответ помещает байт данных на линии Data [0:7].

3. ПУ сигнализирует о действительности байта установкой низкого уровня на линии PtrClk.

4. Хост устанавливает высокий уровень на линии HostBusy, указывая на занятость приемом и обработкой байта.

5. ПУ отвечает установкой высокого уровня на линии PtrClk.

6. Хост подтверждает прием байта импульсом HostCIR.

7. Шаги 1-6 повторяются для каждого следующего байта.

Побайтный режим позволяет поднять скорость обратного канала до скорости прямого канала в стандартном режиме. Однако он может работать только на двунаправленных портах.

Режим ЕРР

Протокол ЕРР (Enhanced Parallel Port - улучшенный парал- лельный порт) был разработан компаниями Intel, Xircom и Zenith Data Systems задолго до принятия IEEE 1284. Он предназначен для повышения производительности обмена по параллельному порту. ЕРР был реализован в чипсете Intel 386SL (микросхема 82360) и впоследствии принят мно- жеством компаний как дополнительный протокол параллель- ного порта. Версии протокола, реализованные до принятия IEEE 1284, отличаются от нынешнего стандарта (см. далее).

Протокол ЕРР обеспечивает четыре типа циклов обмена:

запись данных;

ш чтение данных;

запись адреса;

чтение адреса.

Назначение циклов записи и чтения данных очевидно. Ад- ресные циклы используются для передачи адресной, каналь- ной и управляющей информации. Циклы обмена данными отличаются от адресных циклов применяемыми стробирую- щими сигналами. Назначение сигналов порта ЕРР и их связь с сигналами SPP объясняются в табл. 1.6.

| Контакт | Сигнал SPP | Имя в ЕРР | I/O | Описание | |||||

| 1 | Strobe" | Write# | 0 | Низкий уровень - цикл записи, высокий - цикл чтения | |||||

| 14 | AutoLF# | DataStb# | 0 | Строб данных. Низкий уровень устанавливается в циклах передачи данных | |||||

| 17 | Selecting | AddrStbft | о | Строб адреса. Низкий уро- вень устанавливается в ад- ресных циклах | |||||

| 16 | lnit" | Reset" | о | Сброс ПУ (низким уровнем) | |||||

| 10 | Ack# | INTR# | I | Прерывание от ПУ | |||||

| 11 | Busy | Wait# | Сигнал квитирования. Низкий уровень разрешает начало цикла (установку строба в низкий уровень), переход в высокий - раз- решает завершение цикла (снятие строба) | ||||||

| 2-9 | Data [0:7] | AD[0:7] | I/O | Двунаправленная шина адреса/данных | |||||

| 12 | PaperEnd | AckDataReq* | I | Используется по усмотрению разработчика периферии | |||||

| 13 | Select | Xflag* | I | Используется по усмотрению разработчика периферии | |||||

| 15 | Error# | DataAvail#* | ' | Используется по усмотрению разработчика периферии |

* Сигналы действуют в последовательности согласования (см. далее).

2 Зак.№530

ЕРР- порт имеет расширенный набор регистров (табл. 1.7), который занимает в пространстве ввода/вывода 5-8 смеж- ных байт.

|

Имя регистра |

Смещение |

Режим |

R/W |

Описание |

|

SPP Data Port |

+0 |

SPP/EPP |

W |

Регистр данных SPP |

|

SPP Status Port |

+1 |

SPP/EPP |

R |

Регистр состояния SPP |

|

SPP Control Port |

+2 |

SPP/EPP |

W |

Регистр управления SPP |

|

EPP Address Port |

+3 |

EPP |

R/W |

Регистр адреса EPP. Чтение или запись в него генерирует связан- ный цикл чтения или записи адреса EPP |

|

EPP Data Port |

+4 |

EPP |

R/W |

Регистр данных EPP. Чтение (запись) гене- рирует связанный цикл чтения (записи) дан- ных EPP |

|

Not Defined |

+5...+7 |

EPP |

N/A |

В некоторых кон- троллерах могут исполь- зоваться для 16-/ 32-битных операций ввода/вывода |

Цикл записи данных состоит из следующих фаз:

1. Программа выполняет цикл вывода (IOWR#) в порт 4 (EPP Data Port).

2. Адаптер устанавливает сигнал Write* (низкий уровень), и данные помещаются на выходную шину LPT-порта.

3. При низком уровне Wart# устанавливается строб данных.

4. Порт ждет подтверждения от ПУ (перевода Wait# в вы- сокий уровень).

5. Снимается строб данных - внешний ЕРР-цикл завер- шается.

6. Завершается процессорный цикл вывода.

7. ПУ устанавливает низкий уровень Wait#, указывая на возможность начала следующего цикла.