Протокол передачи данных PC

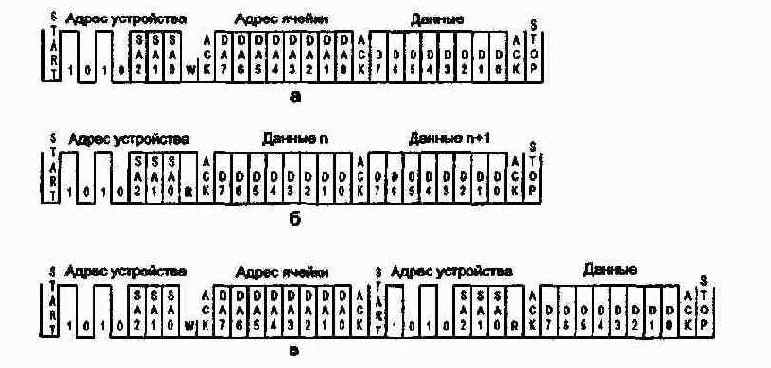

Рисунок 7.12.

Протокол передачи данных PC

Последовательный интерфейс УС обеспечивает двунаправ- ленную передачу данных между парой устройств, исполь- зуя два сигнала: данные SDA (Serial Data) и синхронизацию SCL (Serial Clock). В обмене участвуют два устройства - ве- дущее (Master) и ведомое (Slave). Каждое из них может вы- ступать в роли передатчика, помещающего на линию SDA информационные биты, или приемника. Протокол обмена иллюстрирует Рисунок 7.12. Синхронизацию задает ведущее ус- тройство - контроллер. Линия данных - двунаправленная с выходом типа "открытый коллектор" - управляется обоими устройствами поочередно. Частота обмена (не обязательно постоянная) ограничена сверху величиной 100 кГц для стан- дартного режима и 400 кГц для скоростного, что позволяет организовать программно-управляемую реализацию контрол- лера интерфейса.

Начало любой операции - условие Start - инициируется переводом сигнала SDA из высокого в низкий при высоком уровне SCL. Завершается операция переводом сигнала SDA

из низкого уровня в высокий при высоком уровне SCL - условие Stop. При передаче данных состояние линии SDA может изменяться только при низком уровне SCL, биты дан- ных стробируются положительным перепадом SCL Каждая посылка состоит из 8 бит данных, формируемых передатчи- ком (старший бит - MSB - передается первым), после чего передатчик на один такт освобождает линию данных для получения подтверждения. Приемник во время девятого так- та формирует нулевой бит подтверждения Ack.

После пере- дачи бита подтверждения приемник может задержать сле- дующую посылку, удерживая линию SCL на низком уровне. Приемник также может замедлить передачу по шине на уров- не приема каждого бита, удерживая SCL на низком уровне после его спада, сформированного передатчиком.

Каждое ведомое устройство имеет свой адрес, разрядность ко- торого по умолчанию составляет 7 бит. Адрес А[6:0]

передается ведущим устройством в битах [7:1] первого байта, бит 0 содер- жит признак операции Я1У(Я1/У=1 - чтение, RW=Q

-запись). 7- битный адрес содержит две части: старшие 4 бита А[6:3]

не- сут информацию о типе устройства (например, для EEPROM - 1010), а младшие 3 бита А[0:2] определяют номер устройства данного типа. Многие микросхемы с интерфей- сом PC имеют три адресных входа, коммутацией которых на логические уровни 1 и 0 задается требуемый адрес. Некото- рые значения полного адреса зарезервированы (табл. 7.4).

Общий вызов позволяет включившемуся устройству заявить о себе широковещательным способом. Байт Start

предназна- чен для привлечения внимания процессора к интерфейсу, если в устройстве он организован программным (не аппаратным) способом. До получения этого байта микроконтроллер уст- ройства не опрашивает состояние и не следит за сигналами интерфейса. При использовании 10-битной адресации биты [2:1] содержат старшую часть адреса, а младшие 8 бит будут переданы в следующем байте, если признак RW=0.

Адрес ведомого устройства и тип обращения задается кон- троллером при инициировании обмена. Обмен с памятью иллюстрирует Рисунок 7.13. Здесь SA[0:2] - адрес устройства, DA[0:7] - адрес данных, D[0:7] - данные, W - признак за- писи (0), R - признак чтения (1).

| Биты [7:1] | BKTO(RW) | Назначение |

| 0000 000 | 0 | General call address - адрес общего вызова |

| 0000 000 | 1 | Start. - начало активного обмена |

| 0000 001 | X | Адрес устройства шины CBUS (для сов- местимости) |

| 0000 010 | X | Адрес для устройств иных шин |

| 0000 011 | X | Зарезервировано |

| 0000 1ХХ | X | Зарезервировано |

| 1111 1ХХ | X | Зарезервировано |

| 1111 ОХХ | X | Признак 10-битной адресации |