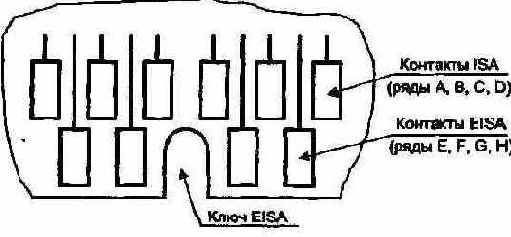

Разъем шины EISA

Рисунок 4.4. Разъем шины EISA

Для режимов EISA используются дополнительные управля- ющие сигналы, обеспечивающие более эффективные режи- мы передачи. В обычном (не пакетном) режиме передачи за каждую пару тактов может быть передано до 32 бит (один такт на фазу адреса, один - на фазу данных). В пакетном режиме (Burst Mode) пакеты данных пересылаются без ука- зания текущего адреса внутри пакета. В пакете очередные данные передаются в каждом такте шины, длина пакета дос- тигает 1024 байт. Шина предусматривает более производи- тельные режимы DMA (см. прил. А4), при которых скорость обмена может достигать 33 Мбайт/с. Линии запросов пре- рываний допускают разделяемое использование, причем со- храняется совместимость с ISA-картами: каждая линия за- проса может программироваться на чувствительность как по высокому (как в ISA), так и по низкому уровню. Шина до-

пускает потребление каждой картой расширения мощности до 45 Вт, но это не означает, что мощность блока питания для 8 слотов должна быть более 360 Вт - полную мощность не потребляет ни один из адаптеров.

Многие решения EISA напоминают МСА. Каждый слот (мак- симум - 8) и системная плата имеют селективное разреше- ние адресации ввода/вывода и отдельные линии запроса и подтверждения управления шиной. Арбитраж запросов вы- полняет устройство ISP (Integrated System Peripheral). При- оритеты (в порядке убывания): регенерация, DMA, CPU, Bus- Master. Обязательной принадлежностью системной платы с шиной EISA является энергонезависимая память конфигу- рации NVRAM, в которой хранится информация об ус- тройствах EISA для каждого слота. Формат записей стан- дартизован, для модификации информации применяется специальная утилита ECU (EISA Configuration Utility). Ар- хитектура позволяет при использовании программно кон- фигурируемых адаптеров автоматически разрешать конфлик- ты, но в отличие от РпР не допускает динамического конфигурирования - после выхода из режима конфигури- рования необходима перезагрузка. Изолированный доступ к портам ввода/вывода каждой карты во время конфигури- рования обеспечивается просто: сигнал AEN, разрешающий декодирование адреса в цикле ввода/вывода, на каждый слот приходит по отдельной линии AENx, в это время программ- но-управляемой.

Так можно обращаться и к картам ISA, но из этого нельзя извлечь выгоды, поскольку они не поддер- живают обмена конфигурационной информацией. Идеи кон- фигурирования EISA были использованы в спецификации РпР для шины ISA (формат конфигурационных записей ESCD напоминает NVRAM EISA).

EISA - дорогая, но оправдывающая себя архитектура, при- меняющаяся в многозадачных системах и на серверах, где требуется высокоэффективное расширение шины ввода/вы- вода. Перед шиной PCI у нее есть преимущество в количе- стве слотов (8 против 4).

Назначение контактов слотов шин ISA и EISA приведено в табл. 4.2 и 4.3.

|

РядР |

Ряд В |

N" |

РЯДА |

РЯДЕ |

|

GND |

GND |

1 |

10СНК |

CMD |

|

+5 В |

Reset |

2 |

Data 7 |

START" |

|

+5 В |

+5 В |

3 |

Data 6 |

EXRDY |

|

Unused |

IRQ 2/9' |

4 |

Data 5 |

EX32# |

|

Unused |

-5В |

5 |

Data 4 |

GND |

|

Key |

DRQ2 |

6 |

Data3 |

Key |

|

Unused |

-12В |

7 |

Data 2 |

EX16# |

|

Unused |

OWS#2 |

8 |

Data1 |

SLBURSTft |

|

+12 В |

+12 В |

9 |

Data 0 |

MSBURST |

|

M/-IO |

GND |

10 |

IOCHDRY |

W/R# |

|

-LOCK |

SmemWR# |

11 |

AENx |

GND |

|

Reserved |

SmemRD# |

12 |

Addr19 |

EMB66#3 |

|

GND |

IOWR# |

13 |

Addi-18 |

EMB133#3 |

|

Reserved |

IORD# |

14 |

Addr17 |

Reserved |

|

ВЕЗ" |

DACK3# |

15 |

Addr16 |

GND |

|

Key |

DRQ3 |

16 |

Addr15 |

Key |

|

BE2# |

DACK 1# |

17 |

Addr14 |

BE 1# |

|

BEO# |

DRQ1 |

18 |

Addr13 |

LA 31 |

|

GND |

Refr" |

19 |

Addr12 |

GND |

|

+5 В |

Bclock |

20 |

Addr11 |

LA30# |

|

LA29# |

IRQ 7 |

21 |

Addr10 |

LA28# |

|

GND |

IRQ 6 |

22 |

Addr 9 |

LA27# |

|

LA26# |

IRQ 5 |

23 |

Addr 8 |

LA25# |

|

LA24# |

IRQ 4 |

24 |

Addr 7 |

GND |

|

Key |

IRQ3 |

25 |

Addr 6 |

Key |

|

LA 16 |

DACK2# |

26 |

Addr 5 |

LA 15 |

|

LA 14 |

TC |

27 |

Addr 4 |

LA 13 |

|

+5 В |

BALE |

28 |

Addr3 |

LA 12 |

|

+5 В |

+5 В |

29 |

Addr 2 |

LA11 |

|

GND |

Osc. |

30 |

Addr1 |

GND |

|

LA 10 |

GND |

31 |

AddrO |

LA9 |

'B4: XT=IRQ2, AT-IRQ9.

8: XT-Card Selected.

12, E13 - только для Fast EISA.

|

РядН |

Ряд О |

N# |

РядС |

Рядб |

|

LA8 |

MCS16# |

1 |

SBHE# |

LA7 |

|

LA6 |

IOCS16# |

2 |

LA 23 |

GND |

|

LA5 |

IRQ 10 |

3 |

LA 22 |

LA4 |

|

+5 В |

IRQ 11 |

4 |

LA 21 |

LA3 |

|

LA2 |

IRQ 12 |

5 |

LA 20 |

GND |

|

Key |

IRQ 15 |

6 |

LA 19 |

Key |

|

Data 16 |

IRQ 14 |

7 |

LA 18 |

Data 17 |

|

Data 18 |

DACKO# |

8 |

LA 17 |

Data 19 |

|

GND |

DRQO |

9 |

MemRD# |

Data 20 |

|

Data 21 |

DACK5 |

10 |

MemWR* |

Data 22 |

|

Data 23 |

DRQ5 |

11 |

Data 8 |

GND |

|

Data 24 |

DACK6# |

12 |

Data 9 |

Data 25 |

|

GND |

DRQ6 |

13 |

Data 10 |

Data 26 |

|

Data 27 |

DACK7# |

14 |

Data 11 |

Data 28 |

|

Key |

DRQ7 |

15 |

Data 12 |

Key |

|

Data 29 |

+5 В |

16 |

Data 13 |

GND |

|

+5 В |

Master* |

17 |

Data 14 |

Data 30 |

|

+5 В |

GND |

18 |

Data 15 |

Data 31 |

|

МАКх# |

- |

19 |

- |

MREQx |

Data[7:0] - шина данных. Addr[19:0] -шина адреса.

т AEN - разрешение адресации портов (запрещает ложную дешифрацию адреса в цикле DMA).

IOWR# - запись в порт. IORD# - чтение порта.

SMemWR-ft - запись в память (в диапазоне адресов 0-FFFFFh).

SMemRD# - чтение памяти

(в диапазоне адресов 0-FFFFFh).

К сигналам запросов прерывания и каналам прямого доступа к памяти относятся следующие:

йй IRQ2/9, IRQ[3:7] - запросы прерываний. Положительный перепад сигнала вызывает запрос аппаратного прерыва- ния. Для идентификации источника высокий уровень должен сохраняться до подтверждения прерывания про- цессором, что затрудняет разделяемое использование пре- рываний.

Линия IRQ2/9 в шинах XT вызывает аппарат- ное прерывание с номером 2, а в AT - с номером 9.

DRQ[1:3] - запросы 8-битных каналов DMA (положитель- ным перепадом).

т DACK[1:3]# - подтверждение запросов 8-битных каналов DMA.

ТС - признак завершения счетчика циклов DMA.

Шина имеет и несколько служебных сигналов синхрониза- ции, сброса и регенерации памяти, установленной на адап- терах:

ш IOCHRDY - готовность устройства, низкий уровень удли- няет текущий цикл (не более 15 мкс).

BALE - разрешение защелки адреса. После его спада в каждом цикле процессора линии Addr 0-19 гарантиро- ванно содержат действительный адрес.

Refr# - цикл регенерации памяти (в XT называется DACK 0#). Сигнал появляется каждые 15 мкс, при этом шина адреса указывает на очередную регенерируемую строку памяти.

т 10СНК - контроль канала. Низкий уровень сигнала вы- зывает NMI CPU (разрешение и индикация в системных портах 061h, 062h).

Reset - сигнал аппаратного сброса (активный уровень - высокий).

BCIock - синхронизация шины с частотой около 8 МГц. ПУ могут не использовать этот сигнал, работая только по управляющим сигналам записи и чтения.

т OSC - частота 14,431818 МГц, несинхронизированная с ши- ной (использовалась старыми дисплейными адаптерами).

Кроме логических сигналов шина имеет контакты для раз- водки питания +5, -5, +12 и -12В.

Дополнительный разъем, расширяющий шину до 16-битной, содержит линии данных, адреса, запросов прерываний и ка- налов прямого доступа:

as Data[15:8] -шина данных. SB HE - признак наличия данных на линиях Data [15:8].

LA[23:17j - нефиксированные сигналы адреса, требующие защелкивания по спаду сигнала BALE. Такой способ по- дачи адреса позволяет сократить время цикла (схемы де- шифратора адреса памяти плат расширения начинают де- кодирование несколько раньше спада BALE).

т IRQ[10:12], IRQ[14:15] - дополнительные запросы преры- ваний.

DRQ[5:7] - запросы 16-битных каналов DMA (положи- тельным перепадом).

т DACK[5:7]# - подтверждение запросов 16-битных каналов DMA.

С переключением разрядности данных связаны сигналы:

MCS16# - адресуемое устройство поддерживает 16-бит- ные обращения к памяти.

IOCS16# - адресуемое устройство поддерживает 16-бит- ные обращения к портам.

К новым управляющим сигналам относятся следующие:

MemWR# - запись в память в любой области до 16 Мбайт.

MemRD# - чтение памяти в любой области до 16 Мбайт.

OWS# - сигнал от устройства, разрешающий системной пла- те укоротить текущий цикл (устранить такты ожидания).

MASTERS - запрос от устройства, использующего 16-бит- ный канал DMA на управление шиной. При получении подтверждения DACK [5:7] Bus-Master может захватить шину (не более чем на 15 мкс).

Обобщенные временные диаграммы циклов чтения или за- писи памяти или ввода/вывода приведены на Рисунок 4.5. Здесь условный сигнал CMD* изображает один из сигналов:

SMEMRD#, MEMRD# - в цикле чтения памяти;

s SMEMWR#, MEMWR# - в цикле записи памяти;

IORD# - в цикле чтения порта ввода/вывода;

IOWR# - в цикле записи порта ввода/вывода.