А.2. Цикл обмена DMA

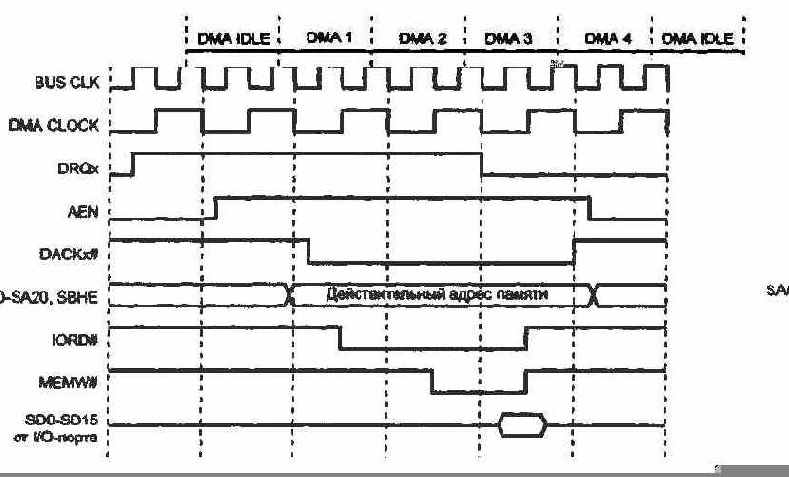

Рисунок А.2. Цикл обмена DMA

Процессор при обмене занят только инициализацией кон- троллера, которая сводится к записи в его регистры несколь- ких байт. Затем обмен производят системная шина и кон- троллер. Если выбранный режим обмена не занимает всей пропускной способности шины, во время операций DMA процессор может продолжать работу.

Прямой доступ к памяти был использован еще в PC/XT, где применялась микросхема четырехканального контролле- ра DMA 18237А. Контроллер имеет 16-разрядные регистры адреса и счетчики, что позволяет программировать переда- чу блоков до 64 Кбайт. Для доступа к пространству разме- ром в 1 Мбайт применили внешние 4-разрядные регистры страниц DMA, отдельные для каждого канала. В них хра- нятся биты адреса А[19:16], а битами А[15:0] управляет кон- троллер. При достижении регистром-счетчиком адреса зна- чения FFFFh следующее его значение будет OOOOh, а внешний регистр адреса страницы останется неизменным. Таким об- разом, если блок начинается не с границы страницы памяти размером в 64 Кбайт, возможно его "сворачивание в кольцо". Но если для процессоров 80х86 в реальном режиме "свора- чиваемые" сегменты могут начинаться с адреса, кратного 10h, то при прямом доступе границы "сворачиваемого" сегмента кратны 1 OOOOh. Этот эффект обязательно необходимо учи-

тывать при программировании прямого доступа - блок, пе- ресекающий границу, должен пересылаться за два сеанса DMA, между которыми канал (включая регистр страниц) должен быть повторно инициализирован.

Из четырех каналов DMA XT на шине ISA доступны толь- ко три (1, 2 и 3). Канал 0 используется для регенерации ди- намической памяти, адрес регенерируемой строки берется с линий адреса ISA. Каналы 1, 2 и 3 обеспечивают побайтную передачу данных и называются 8-битными каналами DMA.

В архитектуре AT подсистему DMA расширили, добавив вто- рой контроллер 8237А. Его подключили к шине адреса со смещением на 1 бит. 16-битные регистры адреса способны управлять линиями адреса А[16:1], младший бит адреса АО всегда нулевой.

Таким образом, второй контроллер передает данные только по два байта, поэтому его каналы названы 16-битными. За один сеанс второй контроллер способен пе- редать до 64 К 16-разрядных слов. Регистры страниц для всех каналов DMA у AT расширены до 8 бит, что делает доступной для любого канала область памяти размером 16 Мбайт (0- FFFFFFh). Эффект "сворачивания" сегментов в каналах пря- мого доступа сохраняется, только для каналов 5, 6 и 7 "коль- ца" имеют размер 64 К слов и границы, кратные 20000h. Микросхемы контроллеров 8237А включены каскадно, и ка- нал 4 недоступен - через него подключается первый контрол- лер. Стандартное назначение каналов приведено в табл. А.3.

Кроме увеличения числа каналов в AT ввели управление тиной ISA - Bus-Mastering - со стороны адаптера. Оно опи- рается на контроллер DMA, выполняющий в данном случае функции арбитра шины. Для получения управления шиной адаптер посылает запрос по линии DRQx (только для кана- лов 5-7) и, получив подтверждение DACKx, устанавливает сигнал MASTERS. Теперь шиной ISA управляет он, но не имеет права занимать шину более чем на 15 мкс за сеанс. В противном случае нарушится регенерация памяти. Интел- лектуальный контроллер может выполнять более эффектив- ные процедуры обмена, чем стандартный DMA.

Управление шиной используют высокопроизводительные адаптеры SCSI и локальных сетей, а также интеллектуаль-

ные графические адаптеры. Однако архитектурой шины до- ступное им пространство ограничено 16 Мбайт.

Ограничения на доступную память для "чистого" режима DMA в новых компьютерах снимаются применением расши- ренных регистров страниц, но об этом должно "знать" ПО.

На шине EISA каналы DMA могут работать в 8-, 16- и 32-битном режиме и, используя все 32 разряда шины ад- реса, иметь доступ ко всей памяти компьютера. Каждый ка- нал программируется на 1 из 4 типов цикла передачи:

Compatible - полностью совместим с ISA.

sii Type A - сокращенный на 25% цикл: время одиночного цикла 875 нс, в блочном режиме время цикла 750 нс.

Ра- ботает почти со всеми ISA-адаптерами с большей скоро- стью.

Type В - сокращенный на 50% цикл (750/500 нс на цикл), работает с большинством EISA-адаптеров и некоторыми ISA. Возможен только с памятью, непосредственно до- ступной контроллеру шины EISA (то есть с памятью на адаптерах EISA и системной, если EISA является основ- ной шиной). Если декодированный адрес памяти отно- сится к 8/16-битной памяти ISA, то контроллер DMA EISA автоматически переводится в режим Compatible.

т Type С (Burst Timing) - сокращенный на 87,5% цикл, ориентированный на пакетный режим передачи. Работа- ет с быстрыми EISA-адаптерами. При обмене 32-битных устройств с 32-битной памятью позволяет развить ско- рость обмена до 33 Мбайт/с.

В PCI-системах для обмена с устройствами системной пла- ты (Fast ATA-2 или E-IDE-порты) возможно использова- ние DMA Type F, при котором между соседними циклами интервал не должен превышать 3 тактов шины (360 нс). Для разгрузки системной шины используется 4-байтный буфер. Режим F может работать только в режиме одиноч- ной передачи или по запросу и исключительно с инкре- ментом адреса. На самой шине PCI адаптеры могут ис- пользовать режим прямого управления шиной, для чего имеется специальный протокол арбитража.

|

Номер канала DMAft |

о |

1 |

2 |

3 |

4 |

5 |

Q |

7 |

|

Стандартное назначение |

XT |

MRFR* |

- |

FDD |

HDD |

Отсутствуют |

||

|

AT |

- |

SDLC* |

FDD |

HDD* |

Каскад |

- |

- |

- |

|

Разрядность, байт |

1 |

2 с четного адреса |

||||||

|

Максимальный размер блока |

64 Кбайта |

128 Кбайт, четный |

||||||

|

Граница блока |

Кратна lOOOh |

Кратна 2000h |

||||||

|

Регистр страниц |

4 бит А16-А19 |

7 бит А17-А23 |

||||||

|

Адреса регистров: страниц начального адреса (W) текущего адреса (R) начального счетчика (W) текущего счетчика (R) |

||||||||

|

087 |

083 |

081 |

082 |

08F |

08В |

089 |

087 |

|

|

000 |

002 |

004 |

006 |

ОСО |

ОСА |

ОС8 |

осе |

|

|

001 |

003 |

005 |

007 |

ОС2 |

ОС6 |

ОСА |

ОСЕ |