Б.2. Подключение устройства к шине ISA

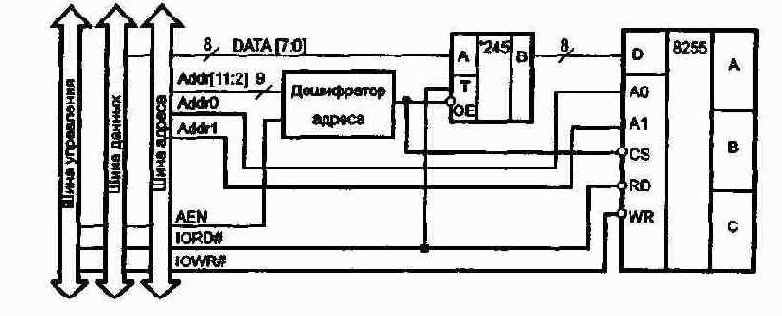

Рисунок Б.2. Подключение устройства к шине ISA

Подключаемое устройство обычно имеет свой буфер дан- ных - двунаправленный приемопередатчик, в качестве ко- торого применяется микросхема 74ALS245 (1533АП6). Бу- фер должен открываться сигналом ОЕ# (Output Enable - разрешение выхода), когда на шине адреса присутствует ад- рес, относящийся к диапазону подключаемого устройства. "Дежурным" направлением передачи является "от шины - к устройству"; переключение в обратную сторону произво- дится по сигналу IORD# шины управления. Таким образом, буфер имеет право передавать данные на шину (управлять шиной данных) только во время действия сигнала чтения, относящегося к зоне адресов данного устройства. Если бы подключаемое устройство было приписано к пространству памяти, в логике управления направлением присутствовал бы сигнал MEMRD#.

Дешифратор адреса предназначен для выявления зоны ад- ресов, относящейся к подключаемому устройству. Если уст- ройству требуется более одного адреса, младшие линии ад- реса (в данном примере - АО и А1) используются для декодирования адреса внутри устройства. Остальные линии поступают на вход комбинационной схемы (или програм- мируемой логической матрицы), которая формирует сигнал

обращения к устройству, называемый CS# (Chip Select). На шинах ISA срабатывание дешифратора адреса должно бло- кироваться высоким уровнем сигнала AEN, сигнализирую- щим о недействительности адреса для порта ввода/вывода в цикле DMA.

Шина управления представлена сигналами IORD# (чтение порта), lOWRft (запись в порт) и AEN. Их состав может быть расширен сигналами обращения к памяти MEMRDft и MEMWR#, а также сигналами запросов прерываний, управления каналами прямого доступа и др. Приведенные четыре сигнала обращения к портам и памяти, используе- мые в шине ISA, характерны для микропроцессорных на- боров и периферийных схем 18080. Есть другой набор сиг- налов - в стиле i8085: сигнал М/10# определяет, к чему относится обращение - к памяти (М) или вводу/выводу (10), сигнал W/R# определяет тип операции - запись (W) или чтение (R), а сама операция осуществляется по неко- торому синхронизирующему сигналу.

Такой способ приме- няется в шинах EISA и PCI.

В микропроцессорной технике применяются прямые и ин- версные логические сигналы. В случае прямых сигналов ло- гическому нулю соответствует низкий уровень сигнала, ло- гической единице - высокий. В случае инверсных сигналов все наоборот. Инверсию сигналов обозначают разными спо- собами: перед названием сигнала ставят знак "минус", над именем проводят черту, после имени ставят обратную ко- сую черту или решетку. В данной книге используется по- следний способ. Управляющие сигналы обычно инверсные. Это так называемые 1(1ог)-активные сигналы, у которых активный уровень сигнала - низкий. Это нужно, чтобы:

повысить помехозащищенность, которая у ТТЛ несим- метричная. Входные токи стремятся подтянуть уровень к высокому, и в случае прямых 7(Дг)-активных сигна- лов это действует согласно с помехой, чреватой ложны- ми срабатываниями. При L-активных сигналах входной ток противодействует помехе. Особенно важно исполь- зовать L-активность для сигналов, передаваемых по ка- белям.

обеспечить возможность нескольким источникам управ- лять одной и той же линией. L-активная линия "подтя- гивается" к высокому уровню резистором, а активный сигнал может вводить любой подключенный к ней вен- тиль с открытым коллектором (можно с тристабильным выходом).

В IBM PC принцип L-активности управляющих сигналов интерфейса был нарушен дважды: Н-активность имеют сиг- налы запросов аппаратных прерываний IRQx и каналов пря- мого доступа DRQx. Это привело к невозможности совмест- ного использования линий прерываний и каналов DMA.

Обозначение и порядок бит и байт шин адреса/данных при- шло от процессоров Intel 8086/88. В шине данных DO обо- значает самый младший бит LSB (Least Significant Bit), а D7 - старший бит байта - MSB (Most Significant Bit). Иногда в опи- сании интерфейсов биты данных обозначаются как D1...D8, при этом младший бит - D1. На рисунках принято старший бит изображать слева, а младший - справа. Обозначение D[7:0] относится к группе сигналов D7, D6,..., D1, DO, a D[0:7] - к тем же сигналам, но в порядке естественной нумерации.В двухбайтном слове, размещаемом в памяти, принят LH-порядок следования: адрес слова указывает на младший байт L (Low), а старший байт Н (High) размещается по адре- су, на единицу большему. В двойном слове порядок будет аналогичным - адрес укажет на самый младший байт, после которого будут размещены следующие по старшинству. Этот порядок естествен для процессоров Intel.

В цифровой схемотехнике есть множество тем для обсужде- ния, остановимся на том, что уже изложено.